电路板设计的基础是设计规则,要确保产品从概念变为可靠实物,关键在于理解且掌握Mentor Xpedition的设计规则设置。本文会深入探究Xpedition设计规则的核心要点,助力大……

电路板设计的基础是设计规则,要确保产品从概念变为可靠实物,关键在于理解且掌握Mentor Xpedition的设计规则设置。本文会深入探究Xpedition设计规则的核心要点,助力大家在实际项目里少走弯路,提高设计效率还有质量。

如何设置层叠结构与阻抗

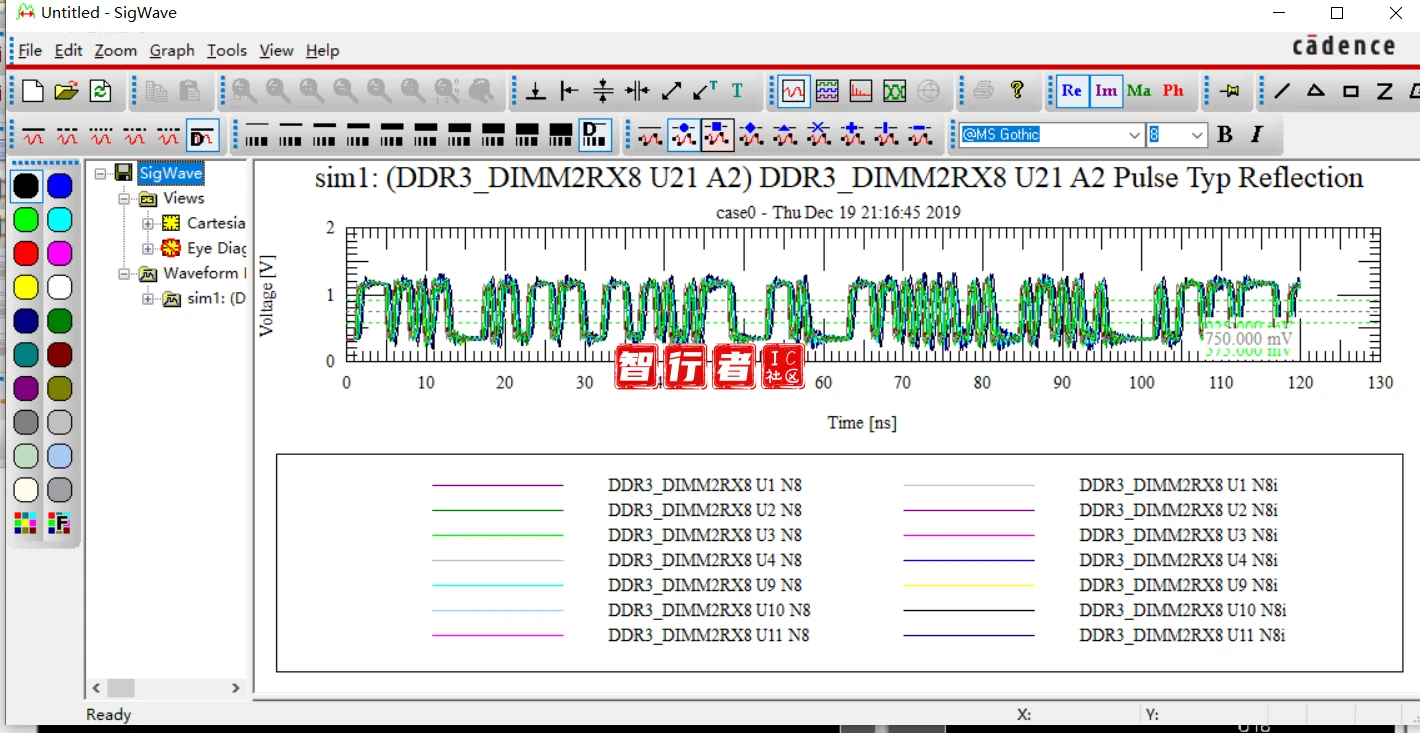

层叠结构作为 PCB 设计的骨架,于 Xpedition 里,借助 Stackup Editor 能够精确界定每一层的材料,以及厚度和铜厚。针对高速信号而言,阻抗控制十分关键。你得依据板厂给出的参数,在规则当中设定目标阻抗值,像单端 50Ω、差分 100Ω这样。软件会依照线宽、线距和介质厚度实时算出实际阻抗,以此确保设计参数跟生产工艺相匹配,从源头保障信号完整性的。

线宽线距最小能做到多少

实际上,这个问题所对应的答案不会是固定不变的数值,它是要视乎你 PCB 制造商具备的能力以及产品所提出的需求的。于 Xpedition 的设计规则当中,你得针对不一样的网络,像普通信号、电源、BGA 出线区,去设置单独的线宽线距约束。举例来说,BGA 区域有可能要求 3.5mil 的极限数值,然而外层空间能够是 6mil。应当一定要在设计的开始阶段跟板厂进行沟通,从而获取他们的制程能力表格,然后再把数据无误地输入到 Clearance Rules 以及 Width Rules 里面。

过孔类型和尺寸怎么选

对于布线可行性以及信号质量而言过孔的选择对其上产生直接影响,Xpedition支持诸如通孔、盲孔、埋孔等多种过孔结构,在规则里你需要依据板厚以及层数去定义不同过孔的钻孔直径还有焊盘尺寸,对于电源网络来说通常要借助较大尺寸的过孔去承载电流,而对于高速信号来讲则应当挑选寄生效应更小的微过孔,合理规划过孔类型并且在规则中为其配备合适的网络类能够自动优化布线路径。

如何设置区域规则约束

常常在一块 PCB 之上,存在着诸多不同的约束需求。比如说那个模拟区域当中,需要更大一些的间距,以此来防止出现干扰情况。而在 BGA 的下方呢,又需要更细的线宽才行。Xpedition 借助那 Area Rules 的功能,十分完美地解决了这个问题。你能够在绘图区域里面,去绘制特定的被划定属于规则层面的区域,像是 Keepin/Keepout 这类,并且针对它单独地设置下来一套完整的电气以及物理规则。当布线活动穿越不同区域的时候,软件就会自动去运用该区域具备的专属约束条文,达成那种细致精准带有优化性质的设计控制效果。

如何检查设计规则确保万无一失

规则设定完毕之后,验证属于不可或缺的环节。Xpedition 的在线 DRC 功能会于你布线之际开展实时检查,将违规项清晰高亮显示出来。布线完成之后,一定要运行批处理 DRC,针对整板实施一次详尽扫描,涵盖短路、开路、间距、未连接线等全部预设规则。这既是交付生产的最后一道防线,又是培养严谨设计习惯的关键一步。

当你于运用Xpedition去开展规则设置操作之时,所碰到的最为令人头疼不已的问题究竟是什么呢,欢迎在评论区域留下话语进行交流探讨,要是觉得本篇文章具备实用价值的话切不可忘记给予点赞以及分享哟!

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~