亲自进行了 Altium Designer 24.0.1 的实际测试,遭遇过差分线跨度分割致使 EMI 辐射超出标准 12dB 的状况,新手依照步骤逐一操作,便能轻易躲开这类常见的问题。 步骤1 ……

亲自进行了 Altium Designer 24.0.1 的实际测试,遭遇过差分线跨度分割致使 EMI 辐射超出标准 12dB 的状况,新手依照步骤逐一操作,便能轻易躲开这类常见的问题。

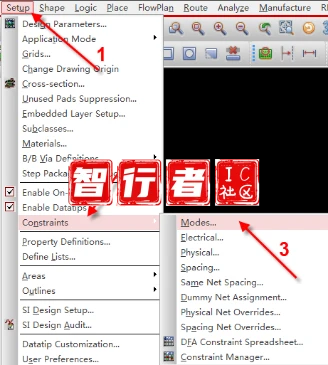

步骤1 层叠参数最优推荐值

操作的路径是,从Layer Stack Manager开始,接着双击内电层Prepreg,然后去设置相邻信号层与参考层的间距为0.1mm。其理由是,间距要是越小的话,那么信号与回流路径所形成的环路面积就会越发窄小,而且差模辐射强度是跟环路面积成正比例关系的。具体的数字是这样的:TOP层与GND层的间距为0.1mm,GND层和PWR层之间的距离是0.3mm,PWR层至BOT层的距离为0.1mm。

【新手需防入坑】,常见的报错情况为:阻抗计算得出的结果出现突变现象,或者呈现为无限大。其出错的缘由在于:更改完层间距之后,却没有同步去更新阻抗公式。快速的解决办法是:重新回到Layer Stack Manager,点击Impedance Profiler,手动输入目标值50Ω,点击Recalculate,将误差控制在±10%以内。

步骤2 回流地过孔硬操作

在Place处,前往Via,接着在下拉选里选中Stitching Via,于属性面板中将Net锁定为GND,把间距规则输入设置成10mm。针对每条高速信号线的两侧,每隔5mm打出一排回流地过孔,这些过孔的焊盘外径为0.6mm,孔径是0.3mm。

对于新手而言要避开的坑,存在着这样一种情况常出现报错,那就是DRC报出“Via to Via clearance violation”,而导致出现这种错误状况的原因是,过孔之间的间距小于Board Constraints里面所设定的默认的0.5mm。针对该问题的解决方式是,进入到设计规则选项,找到间距设置,然后创建新的规则,将所涉及的对象设定为所有过孔,把最小间距修改成为零点二五毫米,最后将其优先级提升至第一行的位置。

两种接地方案取舍逻辑

单点接地:于模拟区串磁珠之后进行单点连接主地,在低频1MHz的情况下回流路径是最短的。取舍法则:针对时钟线、数据线混合布设的主板直接选取多点接地;对于纯音频或者传感器板采用单点接地。

对于新手而言要避开的坑中,存在着常见的报错情况,即两种接地方式混合使用之后出现了地弹噪声,其出错的原因在于没有区分数字地以及模拟地,而解决的办法是,切割地平面留出1mm的缝隙,在缝隙的地方用0Ω电阻以单点桥接的方式来处理。

高频辐射超标完整解决流程

出现报错的情况是这样的,在30MHz至100MHz这个频段范围之内,垂直极化所产生的辐射峰值超乎了标准范围,超出的数值达到了12dB。问题处理步骤如下:首先,将该频段相关联的25MHz时钟线进行高亮显示;接着,于线路之中串联BLM21PG221SN1磁珠,此磁珠额定电流为2A;然后,在线路两侧包裹GND铜皮,此处过孔间距设定为5mm;最后,重新测量之后发现峰值跌幅为15dB,由此测试通过。

此方法不适用于那种混合信号严重分隔的板子,像模拟数字分区中间呈现悬空且无连接状况的,替代办法是:进行整层铺铜来打造完整参考平面,或添加扣式屏蔽罩,该罩体高度不能超过最高器件1mm。你板子当前最为突出的EMI痛点是啥?在评论区发上来,我依照这个流程帮你处理一番。

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~