Cadence 16.6 电子设计全流程实战——从原理图到高速PCB量产(2025最新版) 课程简介 本课程基于Cadence 16.6工具链,覆盖电子设计全生命周期,包含原理图设计(Design En……

Cadence 16.6 电子设计全流程实战——从原理图到高速PCB量产(2025最新版)

课程简介

本课程基于Cadence 16.6工具链,覆盖电子设计全生命周期,包含原理图设计(Design Entry CIS)、PCB封装库开发、高速PCB布局布线、信号完整性优化及生产文件输出等核心环节。通过33+节实战精讲,帮助学员掌握企业级PCB设计规范,独立完成从双层板到六层板(含BGA/DDR3等复杂模块)的设计任务。

课程特色

✅ 模块化知识体系:从焊接工艺到阻抗设计,构建完整知识链条

✅ 真实项目驱动:结合六层板案例解析高速PCB设计要点

✅ 效率优先:详解PCB Editor快捷键、器件定位技巧等实战技巧

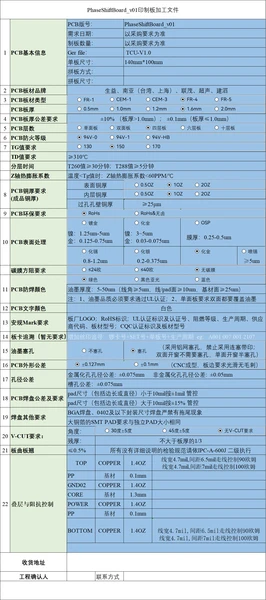

✅ 生产导向:光绘文件生成、叠层阻抗计算等工厂对接技能

课程目录与内容深度解析

第一阶段:基础筑基

- PCB设计基础(§1-2)

- 行业标准解读、Cadence 16.6工作界面解析

- 电子元器件与焊接工艺(§3,7)

- 封装类型识别、焊接可靠性设计要点

- 原理图设计(§4-5,18)

- Design Entry CIS软件操作、网表导出与ERC检查

第二阶段:封装与设计准备

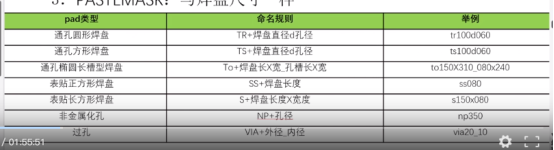

- 封装库开发(§8-9,11-13)

- 原理图符号/PCB封装创建规范、3D模型关联

- PCB设计预处理(§10,19)

- DXF板框导入、叠层结构与物理规则设置(§16)

第三阶段:高速PCB实战

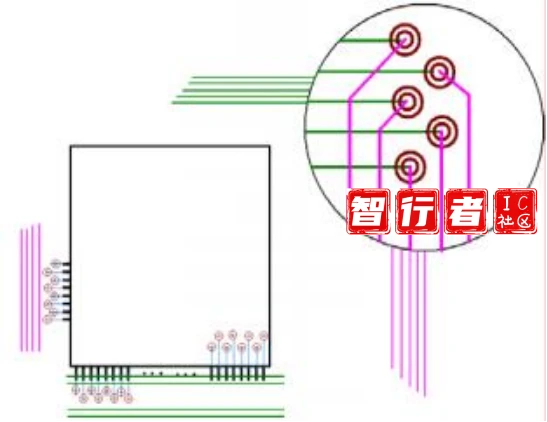

- 布局规划(§21-22,25-27,31-32)

- 双层板与六层板布局策略、电源分区与EMC优化

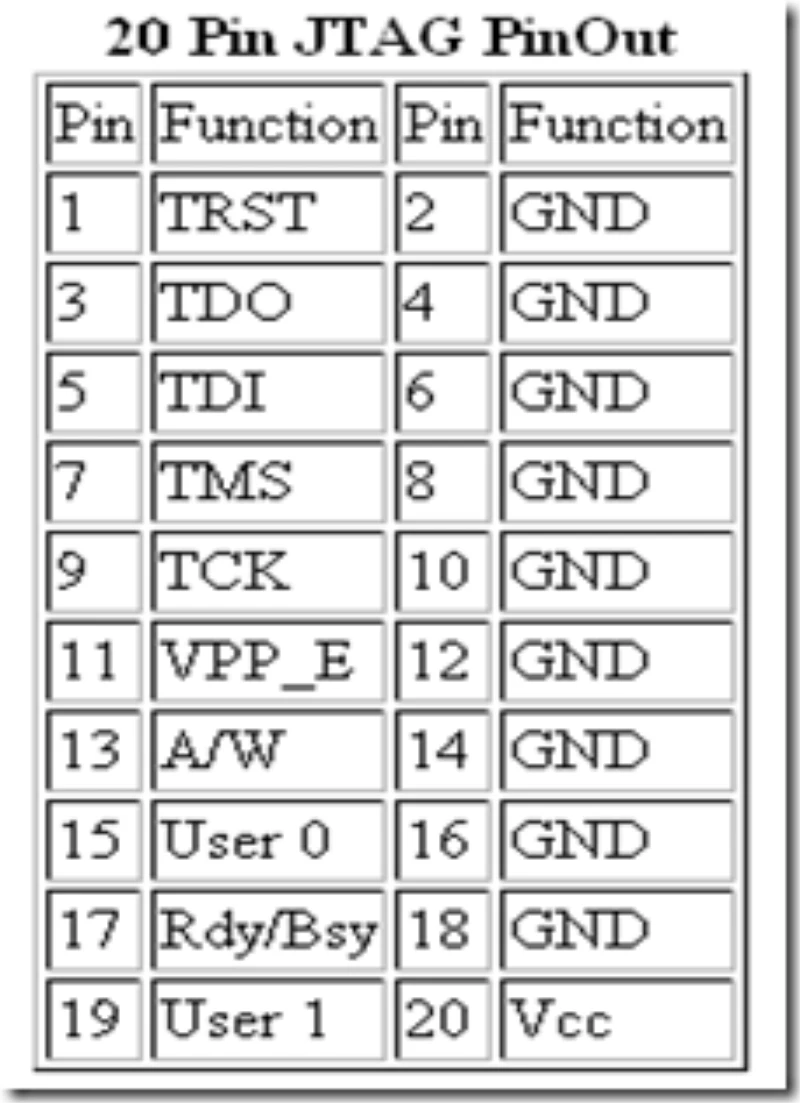

- 布线与信号完整性(§23,28-30,33-35)

- 差分对布线、BGA逃逸布线、DDR3拓扑约束

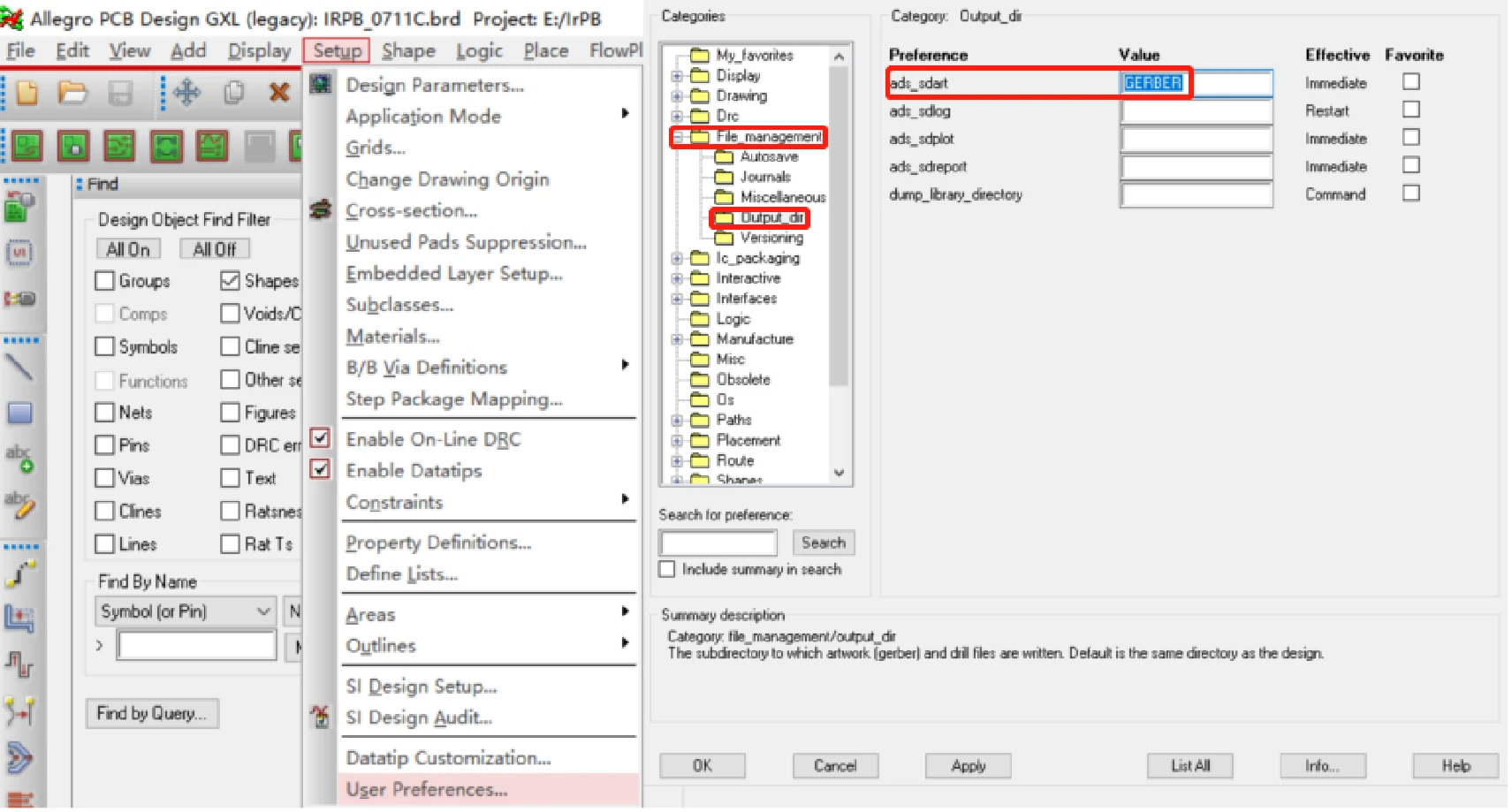

- 生产输出(§24)

- 光绘文件(Gerber)生成与CAM350校验

第四阶段:高阶技巧

- 效率工具(§6,14,17)

- PCB Editor快捷键定制、器件快速定位技巧

- 专项突破(§15,20,36)

- XNet等长组、阻抗计算工具、原理图模块化布局

适合人群

- 硬件工程师:希望系统掌握Cadence 16.6工具链

- PCB设计师:提升高速/多层板设计能力

- 在校学生:积累企业级项目经验

学习成果

? 独立完成6层高速PCB设计(含BGA/DDR3模块)

? 掌握Cadence全工具链协作流程(原理图→PCB→生产文件)

? 输出符合IPC标准的封装库与设计文档

课程服务

- 试看章节:§1-3可免费试学(焊接工艺+软件基础)

- 配套资源:提供课程案例源文件、封装库模板、设计检查清单

- 答疑支持:专属技术群+每月直播答疑(适配学员时区)

微信扫一扫

微信扫一扫

发表评论