摘要 :

一、课程定位与目标

面向人群:PCB Layout 工程师、嵌入式硬件工程师、RK3588 方案开发者、电子设计初学者

核心目标:掌握 RK3588 PCB Layout 核心规范,解决高速信号……

一、课程定位与目标

- 面向人群:PCB Layout 工程师、嵌入式硬件工程师、RK3588 方案开发者、电子设计初学者

- 核心目标:掌握 RK3588 PCB Layout 核心规范,解决高速信号(DDR/PCIe/HDMI/USB3.1)、电源、EMI/EMC、散热等关键设计痛点,实现一次流片成功

- 课程形式:视频教程(分模块实操)+ 图文教程(规范速查)+ 资料包(原厂文档 + 模板 + 检查清单)

二、RK3588 Layout 核心设计要点

(一)基础前提:RK3588 硬件特性与 Layout 约束

RK3588 是 8nm 工艺高

性能 SoC,集成 8 核 CPU、Mali-G610 GPU、6TOPS NPU,支持 LPDDR5、PCIe3.0、HDMI2.1、USB3.1 等高速

接口,Layout 需重点关注

信号完整性(SI)、电源完整性(PI)、电磁兼容(EMC)、散热四大核心。

- 关键约束:

- 高速信号速率高(DDR5 可达 6400Mbps、PCIe3.0 8Gbps),需严格阻抗控制与时序匹配

- 多路电源(核心 VDD_CPU、DDR、IO、PMIC 等),需控制纹波与电源时序

- BGA 封装(通常 FCBGA),引脚密集,需合理扇出与过孔设计

- 典型 TDP 5-15W,需优化散热布局,避免高温影响性能

(二)PCB 叠层与阻抗设计(核心基础)

1. 推荐叠层方案(1.6mm 板厚,8 层通孔板,通用型)

| 层数 |

功能 |

核心作用 |

| TOP |

信号层(高速信号 / 接口信号) |

放置核心器件、高速接口 |

| L2 |

地平面(GND) |

完整参考平面,减少信号干扰 |

| L3 |

信号层(低速信号 / 控制信号) |

布线辅助层 |

| L4 |

电源层(VDD_DDR/VDD_IO 等) |

电源分配,减少压降 |

| L5 |

地平面(GND) |

完整参考平面,隔离电源与信号 |

| L6 |

信号层(高速信号 / 差分信号) |

核心高速信号布线层 |

| L7 |

电源层(VDD_CPU/VDD_GPU 等) |

核心电源分配 |

| BOTTOM |

信号层(低速信号 / 外设信号) |

辅助布线,避免干扰 |

- HDI 方案:10 层 1 阶 / 2 阶 HDI(适用于高密度设计),叠层需保证地平面完整、电源与地相邻,减少电源噪声耦合。

2. 关键阻抗控制标准(必须严格执行)

| 信号类型 |

阻抗要求 |

备注 |

| DDR DQ/DM/ 地址控制信号 |

40Ω±10% |

LPDDR4/LPDDR5 通用 |

| DDR DQS/CLK 差分信号 |

80Ω±10%(可 90Ω) |

差分对内等长≤1ps |

| CKE 信号 |

50Ω±10% |

单端信号,参考地平面 |

| PCIe3.0 差分信号 |

85Ω±10% |

高速差分,少换层 |

| HDMI2.1 差分信号 |

100Ω±10% |

视频信号,屏蔽干扰 |

| USB3.1 差分信号 |

90Ω±10% |

差分对内等长≤5mil |

| 千兆以太网 MDI 差分 |

100Ω±10% |

对内等长≤5mil,对间≤200mil |

| 单端 IO 信号 |

50Ω±10% |

通用 IO,参考地平面 |

- 设计技巧:阻抗计算需结合板厚、介电常数(FR4 常规 4.4)、线宽线距,使用 SI9000 等工具仿真验证,避免凭经验设计。

(三)核心模块 Layout 设计规范(分模块实操)

1. DDR 模块(最核心,故障率最高)

RK3588 支持 LPDDR4/LPDDR4X/LPDDR5,最大

32GB(4×16bit 通道),Layout 直接决定系统稳定性。

- 布局原则:

- DDR 颗粒靠近 RK3588 放置,缩短 DQ/DQS/CLK 走线长度,减少时序偏差

- 同通道 DDR 颗粒对称布局,保证信号等长基础

- ZQ 电阻(240Ω±1%)、ODT_CA 电阻(10kΩ±5%)就近放置在 DDR PHY 引脚旁,避免走线过长

- 电源滤波电容(0.1μF+10μF)就近贴装在 DDR 电源引脚(VDDQ/VDD2/VDD1_1V8),每个电源引脚至少 1 个 0.1μF 电容

- 布线规范:

- 等长控制(关键):

- 同 Byte 内 DQ-DQS、DM-DQS:≤16ps

- 地址 / 控制信号与 CLK:≤16ps

- DQS 与 CLK:≤40ps

- 差分对内:≤1ps,差分对间间距≥3W

- 走线要求:

- 优先在 L2/L6(地平面相邻层)布线,避免跨分割区

- 少换层,过孔数量≤2 个,换层处必须加地回流过孔(30mil 内)

- 不同 Byte 间间距≥2W,同 Byte 内 DQ-DQ 间距≥2W(建议 3W)

- 蛇形走线仅用于等长补偿,间距 > 3W,避免串扰

- 电源设计:

- VDD_DDR/VDDQ_DDR/VDD2_DDR:≥6 个 0503 过孔,保证载流能力

- VDD1_1V8_DDR:≥2 个 0402 过孔

- 电源平面避免割裂,保证回流路径完整

- 常见陷阱:DQ/CA 信号线对调(不支持)、ZQ 电阻精度不够、电源平面割裂、差分线不等长、过孔延时忽略。

2. 电源模块(PI 核心,决定系统稳定性)

RK3588 需多路电源供电,推荐搭配 RK806/RK809 PMIC,简化电源设计,支持 DVFS 动态调压。

- 布局原则:

- PMIC 靠近 RK3588 放置,缩短核心电源(VDD_CPU/VDD_GPU)走线,减少压降

- 电源滤波电容(去耦电容)就近贴装在 RK3588 电源引脚,BGA 引脚下方可放置埋容

- 电感、二极管等发热器件远离高速信号与热敏元件,避免热干扰

- 电源地与信号地分开,单点连接(避免地环路)

- 布线规范:

- 核心电源走线宽短,载流能力满足最大电流(VDD_CPU≥2A,需计算线宽)

- 电源平面分割清晰,避免不同电源域交叉

- 反馈线(FB)直接连接到输出电容端,避免经过噪声区域

- 电源时序:按 “先 IO 电源→核心电源→DDR 电源” 顺序上电,避免芯片损坏

- 关键检查:电源纹波≤50mV,核心电源压降≤3%,电源地阻抗≤10mΩ

3. 高速接口模块(PCIe/HDMI/USB3.1 / 以太网)

(1)PCIe3.0

- 差分线(TX/RX)100Ω 阻抗,对内等长≤5mil,对间等长≤20mil

- 走线远离时钟信号、电源噪声源,间距≥3W

- 少换层,过孔≤1 个,换层处加地回流过孔

- 终端电阻(100Ω)就近放置在接收端,避免走线过长

(2)HDMI2.1

- 差分线 100Ω 阻抗,对内等长≤3mil,屏蔽层接地良好

- HDMI 接口靠近板边放置,ESD 器件(TVS 管)就近贴装在接口引脚旁

- 走线避免与高频信号(WiFi / 蓝牙)并行,间距≥5W

- 连接器接地引脚多打过孔,连接地平面,增强屏蔽

(3)USB3.1

- 差分线 90Ω 阻抗,对内等长≤5mil,对间等长≤50mil

- USB3.1 与 USB2.0 信号分开布线,避免干扰

- 电源(VUSB)走线宽短,滤波电容就近贴装

- ESD 器件靠近接口放置,保护芯片免受静电损坏

(4)千兆以太网

- MDI 差分线 100Ω 阻抗,对内等长≤5mil,对间≤200mil

- 网变(变压器)靠近 RJ45 接口放置,下方禁止布线,铺地隔离

- RGMII 信号以 TX/RXCLK 为等长依据,数据与时钟等长≤120mil

- 防护器件(TVS / 压敏电阻)靠近 RJ45 接口,浪涌防护优先。

4. 存储模块(eMMC/NVMe)

- eMMC 5.1:

- 支持 HS400 模式,信号少换层,过孔≤2 个,换层处加地回流过孔

- 数据信号(DATA0-7)与时钟(CLK)等长≤50mil,单端 50Ω 阻抗

- 电源滤波电容就近贴装,避免电源噪声影响读写速度。

- NVMe SSD:

- PCIe3.0 接口,遵循 PCIe Layout 规范,差分线 85Ω 阻抗

- SSD 接口靠近 RK3588 PCIe 引脚放置,缩短走线

- 电源(VCC)走线宽短,滤波电容充足,避免掉电导致数据丢失

5. 散热与 EMI/EMC 设计

- 散热设计:

- RK3588 下方铺大面积地铜,增加散热面积

- 核心发热区域(CPU/GPU/NPU)预留散热片 / 风扇安装位置,避免覆盖元件

- 热敏感元件(晶振、传感器)远离发热器件,间距≥5mm

- 多层板地平面连通,增强散热传导能力。

- EMI/EMC 设计:

- 高速信号走内层,避免表层辐射

- 接口处加滤波电容 / 磁珠,抑制共模噪声

- 晶振(24MHz/32.768kHz)靠近芯片引脚,下方铺地,屏蔽罩覆盖

- 无线模块(WiFi / 蓝牙)单独分区,屏蔽罩接地良好,避免干扰其他信号

- 地平面完整,避免分割,减少地环路噪声。

(四)Layout 流程与检查清单(实操步骤)

1. 标准 Layout 流程

- 前期准备:获取 RK3588 datasheet、硬件设计指南、原理图,确认叠层与阻抗方案

- 布局规划:划分核心区域(CPU/DDR/PMIC)、高速接口区域、低速外设区域,遵循 “核心优先、高速就近” 原则

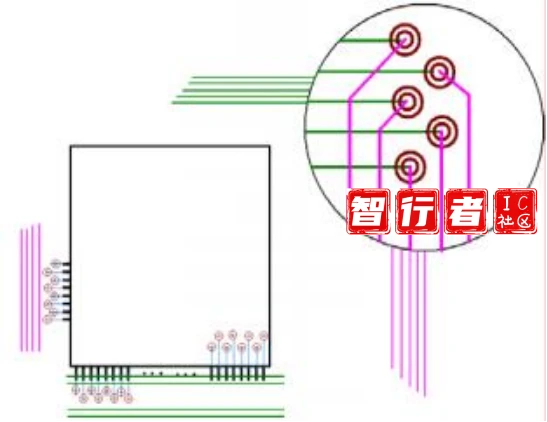

- 扇出设计:BGA 引脚扇出采用 “十字扇出”,过孔尺寸(8-12mil)满足工艺要求,避免过孔密集导致短路

- 核心布线:优先布 DDR、PCIe、HDMI 等高速信号,严格控制阻抗与等长

- 电源布线:布核心电源、滤波电容,保证电源完整性

- 低速布线:布 IO、控制信号,避免干扰高速信号

- 铺铜与接地:大面积铺地,地过孔均匀分布,保证地平面完整

- DRC 检查:检查线宽、线距、过孔、阻抗、等长等,消除违规

- SI/PI 仿真:对高速信号进行时序、阻抗仿真,对电源进行纹波仿真

- 输出文件:生成 Gerber、BOM、坐标文件,提交生产

2. 关键检查清单(必查项)

| 检查类别 |

核心检查项 |

合格标准 |

| 阻抗检查 |

所有高速信号阻抗 |

符合设计标准,误差≤10% |

| 等长检查 |

DDR/PCIe/HDMI 等长 |

符合时序要求,无超差 |

| 电源检查 |

电源纹波、压降、载流 |

纹波≤50mV,压降≤3%,线宽满足载流 |

| 过孔检查 |

过孔数量、尺寸、回流过孔 |

高速信号过孔≤2 个,换层处加地过孔 |

| 布局检查 |

核心器件位置、滤波电容位置 |

高速器件就近,电容贴装引脚旁 |

| EMI 检查 |

屏蔽、滤波、地平面 |

无地环路,接口滤波完善 |

| 散热检查 |

发热区域布局、散热面积 |

核心区域散热良好,无热聚集 |

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~