有本人亲自进行的关于Altium Designer 22.6.1的实际测试,经历过在进行差分对等长绕线之后阻抗径直飞走的状况,对于新手而言,只要依照步骤循序渐进地开展操作,便能够轻……

有本人亲自进行的关于Altium Designer 22.6.1的实际测试,经历过在进行差分对等长绕线之后阻抗径直飞走的状况,对于新手而言,只要依照步骤循序渐进地开展操作,便能够轻易地躲开这类常见的问题情况。

设置线宽与阻抗匹配值

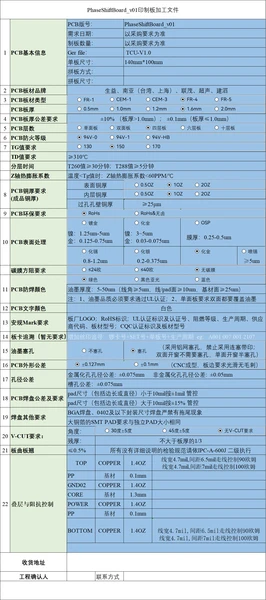

找寻到规则管理器之中的Design Rules,而后进入Routing Width,着手去新建一个网络类,将差分对线宽设定为0.127mm(5mil),同时把线距设定为0.127mm。此参数面向板厚1.6mm、铜厚1oz、介电常数4.2的FR4板材而言,能够实现90Ω差分阻抗的稳定控制。

针对新手而言,需要避开的坑是,常见的报错呈现为“Impedance Mismatch”这样的警告,其缘由在于,你仅仅对线路宽度进行了更改,却没有变动参考层之间的距离。能够快速达成解决的办法是,在Layer Stack Manager当中,将相邻参考层的厚度调节为统一的0.2mm,之后再次运行SI仿真进行验证。

过孔盖油还是开窗

开启Place Via,设定过孔内径为0.3mm、外径为0.6mm。对两种方案予以对比:方案A盖油,即勾选“Tented”复选框,此适合BGA密集区域用以防止短路;至于方案B开窗,也就是不勾选它,这适合测试点或者散热孔。BGA下方必定得采用盖油,不然锡珠会胡乱滚动;电源模块周围采用开窗,以便于万用表勾测。

新手要避开这个坑,报错“Via Tent Missing”表明工厂遗漏了盖油,其缘由是Gerber没有输出阻焊层,前往File Fabrication Outputs Gerber,去确认“Include Solder Mask”打了钩,并且Via Tent对应的层选中了Top/Bottom Solder Mask。

修复高频短路报错

报错之中最为常见的完整形式呈现为“Short-Circuit Between Net GND and Net VCC on Pad R1-2”。存在着一站式解决的流程 ,首先要按下Shift+S进行单层高亮 ,依据报错坐标朝着两边去寻找 ,大概有八成的可能性是旁路电容下方的焊盘出现连锡情况。运用快捷键Ctrl+H来选择整个网络 ,查看哪一个铜皮呈现出异常的凸起。当找到之后切换到PCB Editor ,借助Slice Tracks工具沿着焊盘边缘切除0.2mm ,之后再次运行DRC。

菜鸟需防踩雷要点:千万别直接去删除铜皮然后重新绘制,因为这样极易遗漏掉隐蔽的过孔。正确的操作方法是,先进行Tools Design Rule Check然后Batch Run,接着记录下所有产生冲突的坐标 做完这些操作之后再去批量修正,修正完毕后再次运行Clearance规则,一直到绿色对号出现为止。

这一招针对于两层板以及四层板而言极为有效,然而要是你所运用的是六层以上的背板,并且内层存在埋盲孔,那么DRC误报的几率将会大幅度增高。替代的办法是直接将ODB++导出,交付给工厂去进行飞针测试,千万别自己一味去死磕。你碰到过哪一种报错是修改了三次依旧没能摆平的呢?在评论区抛过来,我来帮你瞅瞅。

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~