关于Cadence 17.4 Allegro PCB Editor,我亲自进行了实际测试,遇到了“差分对等长约束怎么都不产生效果、绕线之后仍然出现报错”这样的麻烦情况,对于新手而言哟,只要依……

关于Cadence 17.4 Allegro PCB Editor,我亲自进行了实际测试,遇到了“差分对等长约束怎么都不产生效果、绕线之后仍然出现报错”这样的麻烦情况,对于新手而言哟,只要依照下面的步骤一个一个地去进行操作,便能够轻快地避免这类平常会出现的问题啦。

设置差分对属性

进到Constraint Manager(快捷键为 CM所在处)里面,在左侧那些导航栏中去选取Electrical Constraint Set,之后再去点击Differential Pair。在空白的地方通过右键点击选择Create Differential Pair,接着按住Ctrl键同时进行多个网络这种选择(像是P以及N),最后点击OK。把8mil填入Primary Gap,将5mil填入Primary Width,这是最为常用的100欧姆阻抗基础值。

【新手需防入坑】,常见会出现报错情况:“Net not found” ,或者是无法成功创建对。其核心的原因在于:两个网络名称呈现出无规律状态,比如说USB_DP和USB_DN缺少了_N后缀。能够快速得以解决的办法是:先于原理图之中将命名后缀统一为_D和_N,接着重新去生成网表之后再进行导入。

设置等长匹配规则

此刻依旧处于Constraint Manager之中,切换至Electrical这一项,接着进入Net,再进入Routing,然后是Relative Propagation Delay。挑选出你刚才才创立的差分对,用鼠标右键点击Create,再点击Pin Pair,从中选定驱动端以及接收端焊盘。设Target为最长的那根线,填Tolerance为5mil(1mil等于0.0254mm中的0.0254mm),点击Analyze检查是否生效。

【新手需留意避开技术陷阱】,存在这样一种较为常见的状况:已经对Tolerance进行了设置,然而在完成绕线操作之后,DRC却依旧呈现报红的情况。而其最为关键的原因在于:并没有勾选“Use Relative Propagation Delay”这一排他性的全局开关。采取的解决方式为:返回至CM的最高层级,寻觅到Analysis Modes,进而找到其中的Electrical Modes,将Relative Propagation Delay由Off转变为On。

关键参数推荐值

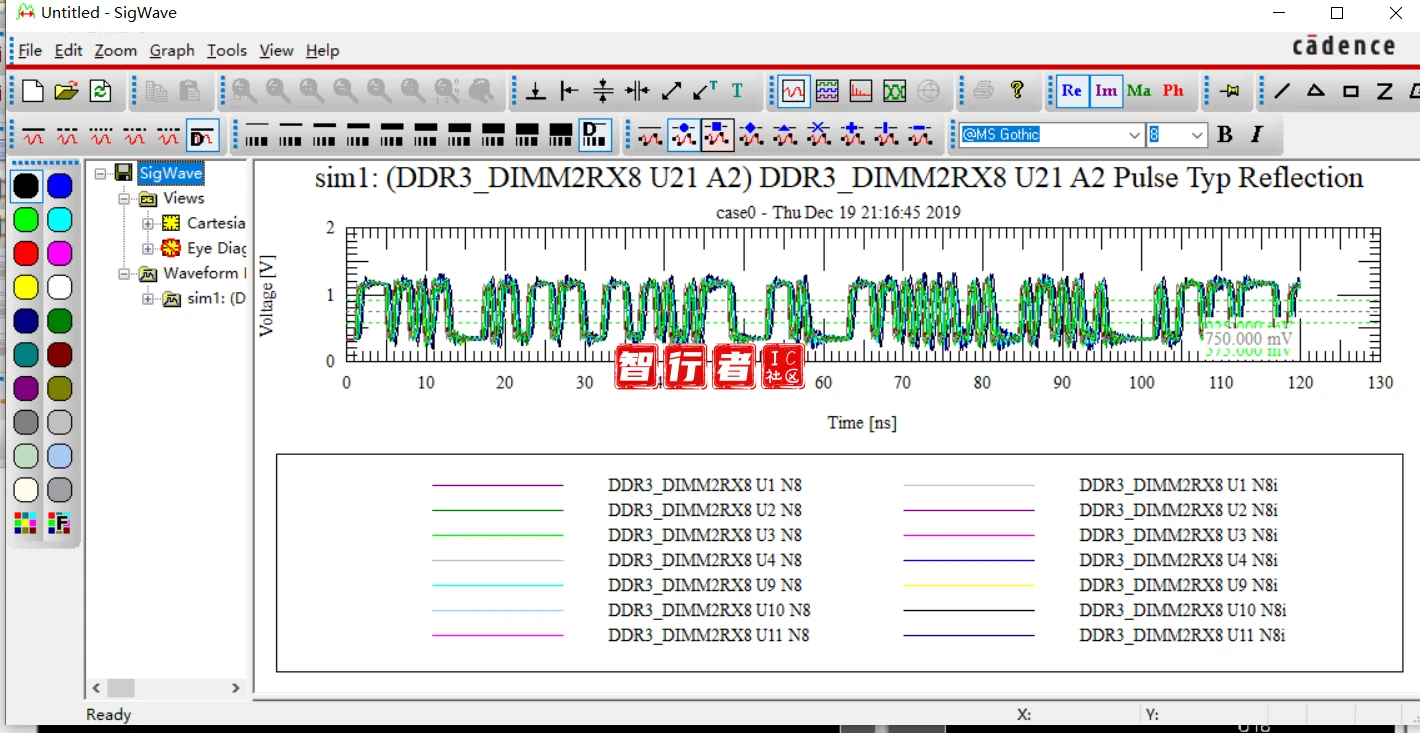

对于差分对耦合长度而言,推荐的数值是100mil。其具备这样的理由:当低于80mil这个数值的时候 ,信号回流路径呈现出不完整的状态 ,进而容易引入共模噪声 ;当高于150mil的时候 ,会占用过多的布线空间 ,并且对于板材均匀度有着较高的要求。实际上对100mil进行测试 ,能够在四层板 、1.6mm厚度的情况下 ,让眼图张开度保持最佳状态。

两种绕线方案对比

方案A情况为,自动绕线,也就是Route之后选择Auto-Route再选Differential Pair,它适用于那种状况,即处于密集BGA区域,并且在人工绕线容易出现错误的时候。方案B的情况是,手动滑动,也就是Route之后选Slide,然后右键选中Diff Pair Tune,它适合于当高速信号也就是大于5Gbps的信号,在需要精确控制每段长度的情形下。舍弃与选取的逻辑是,要是工期紧张那就选择A,要是信号完整性具有优先属性那就选择B;若是混合使用就会将绕线的算法弄乱,严格禁止在同一条线上交替进行使用句号。

高频报错一站式解决

出现了这样的报错信息,这里的报错信息是“DRC error: ‘L/L’ or ‘P/P’ violation on diff pair”,还有完整流程,这里的完整流程是。

1. 把Constraint Manager关闭掉,将所有绕线都删除掉,通过Edit菜单选择Delete选项,在Find栏那里只勾选Clines。

2. 开启Setup,接着进入Constraints,再进入Modes,将Diff Pair Phase Tolerance设置成Off。

3. 重新按步骤二设置等长,再打开On。

4. 重新进行绕线操作,在绕线完成之后马上跑去Tools → Quick Reports → Diff Pair Phase Report那里,去确认最大偏差情况。

5. 若出现再次报错的情况,运用DB Doctor对数据库予以清理(操作步骤为File → Database → DB Doctor),随后重新启动软件。

这个方法,对于Cadence 16.6以及更早的版本是不适用的,因为其约束管理器界面存在差异,对于柔性板或者铝基板同样不适用,这是由于阻抗计算需要重新标定。替代的解决办法是,要么升级到17.4以上的版本,要么改用Sigrity来进行全板阻抗的设置之后再调整参数。你在实际操作的时候,有没有碰到过“绕完线之后相位差反而变大”这种奇怪的事情呢?在评论区大家一同进行排查。

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~