有人亲自测试了Altium Designer 24,遭遇过铺铜与器件距离太近致使板子短路的情况,不过新手只要依照步骤一步步去操作,便能轻易躲开这类常见问题。 句号是对的吧,我是……

有人亲自测试了Altium Designer 24,遭遇过铺铜与器件距离太近致使板子短路的情况,不过新手只要依照步骤一步步去操作,便能轻易躲开这类常见问题。 句号是对的吧,我是按照要求改写句子,不太确定你说的句末标点符号非要用逗号,要是有问题你可以再跟我说。

第一步 设置安全间距规则

点开Design菜单之中的Rules选项,于Electrical类别之内寻觅Clearance。创建一条专为Polygon定制的规则,将约束条件里的最小间距径直变为0.25mm。此数值可兼顾常规板厂加工能力以及信号隔离需求,设置完毕后要把新规则的优先级调至最高。

【新手避坑】

好多人仅仅修改变了全局之间的距离,然而在进行铺铜操作之际却发觉规则根本就没有产生效用。这个原因在于软件会优先去执行具有较高优先级的规则,一定要将新创建的Polygon规则拖动到最上方,不然的话软件会继续采用默认的0.2mm间距,处于高速信号或者高压的区域很容易引发短路现象。

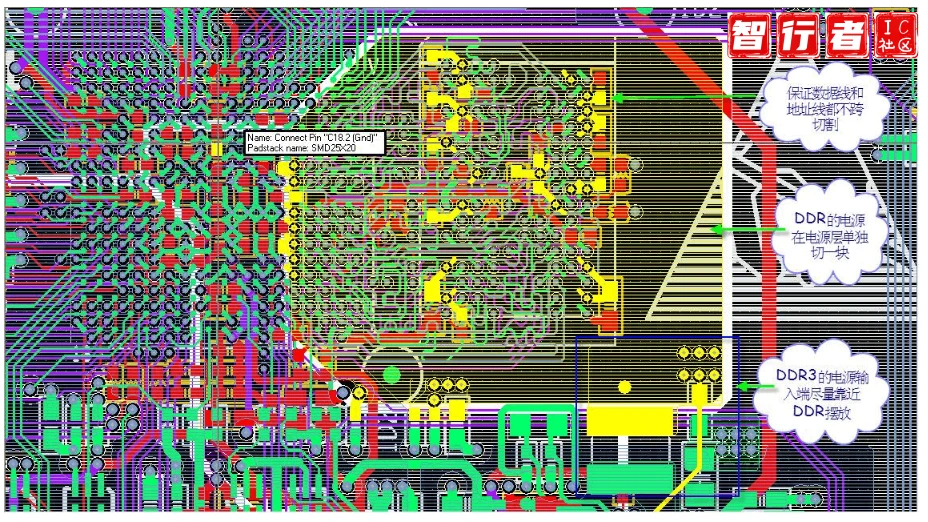

第二步 执行铺铜并关联规则

返回PCB界面之后,点击Place菜单,从中选择Polygon Pour。于属性面板当中,将要“Remove Dead Copper”勾选上,它能够自动清理孤立铜皮。最为关键的一步是,在Net Options里选定目标网络后,要确保下方的“Clearance”栏已经去调用刚才新建的0.25mm规则。

【新手避坑】

倘若铺展出来发觉间距未曾改变,大概率是没有正确关联规则。此时能够通过右键点击铺铜区域,选择Properties,来检查规则名称是否相符。此外,大面积的地铜建议采用实心填充方式,而信号层的铜皮则采用网格填充方式,这两者在散热以及抗干扰能力方面存在很大差别,要是选错了,焊接的时候容易出现起泡现象。

第三步 手动微调与避让

铺完铜后,针对芯片引脚密集之处,于Tools菜单中将Convert打开,选取“Explode Polygon to Free Primitives”把铜皮进行打散。借助快捷键M向着V移动,搭配G对捕捉栅格予以调整,手动把铜皮边缘推至距离器件焊盘起码0.2mm的地方。

【新手避坑】

机械结构中的接插件外壳,或者定位孔之类的,自动铺铜没办法全部识别,要是遗漏了这些位置,在进行装配的时候,铜皮就有可能直接把板子给刮破。一旦碰到报错显现出没“Short Circuit Detected”这种情况,直接去打开Reports里面的Board Information,把“Report Violations”勾选起来,如此就能迅速定位出所有间距不够的坐标点。

关键参数取舍指南

0.25毫米,是我于2盎司铜厚板子之上的最具优势推荐数值,相较于常规的0.2毫米而言,多预留了安全裕度。倘若你处于射频模块或者高频信号区域,建议将同一网络的间距也调整至0.3毫米,虽说会占据一定空间,然而却能够切实减少寄生电容;普通电源板采用0.2毫米亦是可行的,条件是板厂工艺得以提供支持。

此方法于常规FR – 4板材、板厚为1.6mm的情形下经过实测呈现出有效性,然而并不适用于刚挠结合板或者厚度在0.5mm以下的超薄板。一旦碰到这类状况,要直接依据厂家所提供的“DFM设计规范”再次运行一遍规则,切勿强行套用这个数值。

是否曾遭遇铺铜之后割线补刀时那令人尴尬的处境呢?在评论区里交流交流你应对的办法吧。

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~