在 Cadence Allegro 设计流程中,原理图封装库(.olb)是连接电路逻辑与 PCB 物理实现的核心基础。一套规范、统一、可复用的封装库,能大幅提升设计效率、降低 BOM ……

一、Allegro 元件库体系架构

1. 库文件类型与路径

-

PCB 封装库:包含 .pad(焊盘)、.dra(封装绘图)、.psm(封装模型),存放于 share\pcb\pcb_lib\symbols 路径。

-

系统标准库:

-

CAPSYM.olb:电源、地、标题栏等非实物符号。

-

DISCRETE.olb:电阻、电容、电感等无源器件。

-

CONNECTOR.olb:USB、HDMI 等连接器符号。

2. 企业级库管理原则

-

版本控制:库文件命名含版本号(如 MCU_LIB_V1.0.olb),配合 Git/SVN 管理迭代,方便团队协作追溯。

二、原理图封装库创建标准流程

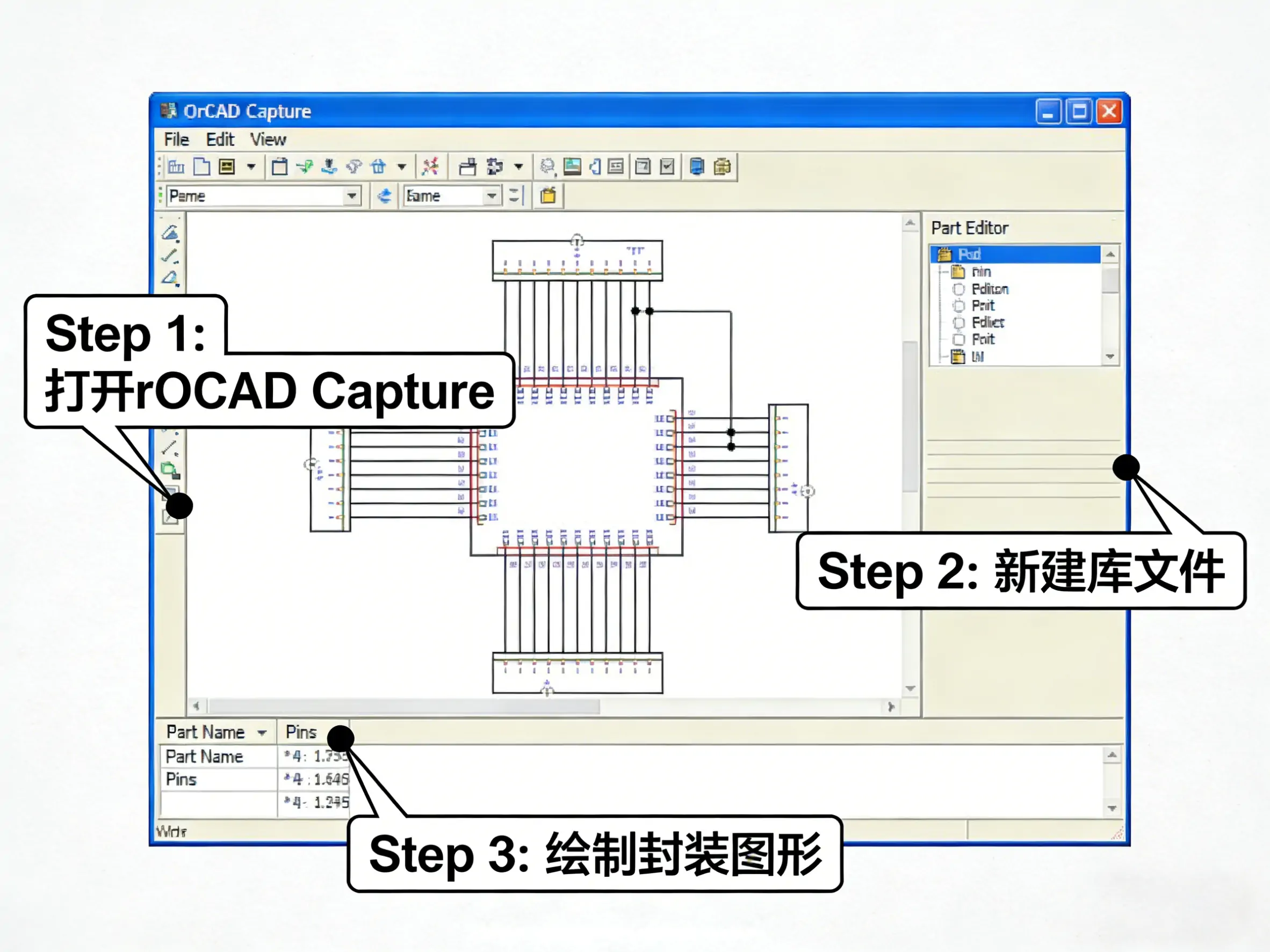

1. 新建原理图库文件

-

打开 OrCAD Capture,执行 File → New → Library,生成默认 library1.olb。

-

右键库文件 → Save As,选择无中文、无空格路径,重命名为规范名称(如 HW_Component_Lib.olb),这里提醒大家,中文路径是建库中最常见的错误,智行者IC社区很多新手都曾踩过这个坑。

-

配置库路径:Options → Preferences → Library,添加自定义库路径,确保软件可正常调用。

2. 新建元件符号(New Part)

|

参数项

|

示例

|

|

|

Name

|

元件型号/通用名,大写、无特殊字符

|

STM32F103C8T6

|

|

Part Reference Prefix

|

位号前缀,行业标准

|

U(IC)、R(电阻)、C(电容)

|

|

PCB Footprint

|

关联 PCB 封装名,与 .psm 一致

|

LQFP48

|

|

Parts per Pkg

|

单封装内元件数(如运放 4 合 1)

|

1

|

|

Pin Number Visible

|

勾选,确保引脚编号可见

|

勾选

|

|

Package Type

|

选择对应封装类型

|

Standard

|

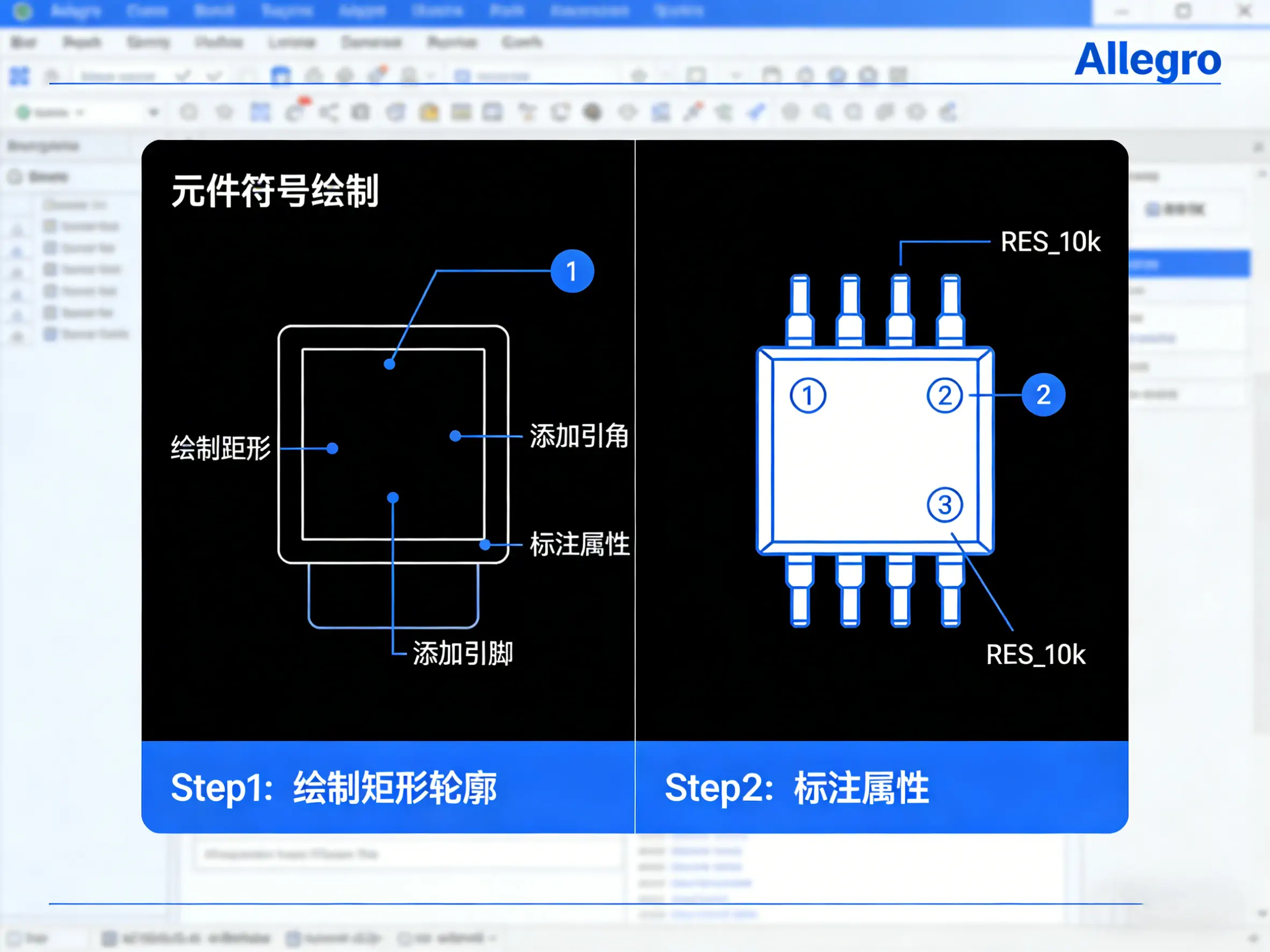

3. 元件符号绘制规范

(1)引脚定义与布局

-

引脚编号:必须与 datasheet 及 PCB 封装引脚编号完全一致,不可自定义、跳号,这是避免后续网表报错的关键,智行者IC社区多次提醒工程师重视这一点。

-

引脚类型:按电气属性设置(Edit → Pin):

-

Input:输入引脚

-

Output:输出引脚

-

Power:电源/地引脚(VCC、GND)

-

Bidirectional:双向引脚(I/O)

-

Passive:无源器件引脚(电阻、电容)

-

电源引脚(VCC)放顶部,地引脚(GND)放底部,信号引脚按功能分组排布。

-

引脚间距统一为 100 mil,便于连线与可读性。

-

复杂 IC 按功能块(如 GPIO、SPI、UART)分区,减少交叉连线,这也是智行者IC社区工程师分享的实战技巧。

(2)符号外形与标注

-

绘制矩形轮廓(Place → Rectangle),尺寸适配引脚数量,边框线宽 10 mil。

-

第 1 引脚标识:在轮廓左上角添加圆点/三角,标注 PIN 1,与 PCB 封装极性一致,避免焊接时极性错误。

-

元件名称:放置于轮廓上方,字体 ROMAN,高度 40 mil,线宽 6 mil,确保清晰可读。

4. 元件属性定义(关键规范)

-

双击元件 → Edit Properties,添加/编辑以下属性:

-

Value:元件参数值(如 10K、0.1uF),无源器件必填。

-

Manufacturer:厂商名称(如 ST、TI)。

-

MPN:物料编码(关键,用于 BOM 与采购匹配)。

-

Description:功能描述(如 32 位 MCU、LDO 稳压器)。

-

PCB Footprint:必填且准确,关联对应 PCB 封装(如 SOT23-3),否则会导致 PCB 导入报错。

-

批量属性设置:选中同类元件 → Edit → Properties,统一赋值,提升效率,适合批量建库场景。

5. 多单元元件(Multi-Unit Part)创建

-

New Part 时,Parts per Pkg 设为 4,Part U 设为 A/B/C/D。

-

分别绘制 4 个单元符号,引脚定义与 datasheet 一致。

-

公共引脚(VCC、GND)仅在一个单元定义,其余单元继承,避免重复,减少冗余。

三、原理图封装库设计核心规范

1. 命名规范(强制标准)

(1)库文件命名

(2)元件命名

-

通用器件:[类型]_[参数]_[封装] 示例:R_10K_0603、C_0.1UF_0805

-

IC/定制器件:[型号]_[封装] 示例:STM32F103C8T6_LQFP48、TPS54331_SOT23-5

-

禁止字符:!@#$%^&*()空格.,仅用 A-Z、0-9、_,这是智行者IC社区总结的避坑要点,避免软件识别异常。

(3)引脚/网络命名

-

信号名:大写、有意义,用 _ 分隔(如 SPI_CLK、UART_TX),便于后期调试。

-

低电平有效:后缀 _N(如 CS_N、RESET_N),统一规范,避免混淆。

-

差分信号:+/- 结尾(如 USB_DP、USB_DM),不建议用 P/N,这是智行者IC社区工程师推荐的命名方式。

-

电源/地:VCC_3V3、GND、AGND(模拟地)、DGND(数字地),区分模拟与数字地,减少干扰。

2. 符号绘制规范

-

尺寸统一:基础元件(电阻、电容)符号尺寸 100×50 mil,IC 按引脚数量适配,保持视觉统一,提升原理图可读性。

-

文本规范:

-

位号(Ref Des):字体 ROMAN,高度 30-40 mil,线宽 5-8 mil,不重叠、不覆盖引脚。

-

元件值:放置于符号旁,清晰可读,便于后期核对。

-

引脚直接分叉,需引出后再分支。

-

文字倒置、重叠,所有文字方向统一(向上/向左)。

-

跨页符号(Off-Page)翻转使用,需与信号流向一致。

3. 引脚与电气规范

-

未用引脚:标注 X,设置为 Passive 类型,避免 DRC 报错,这是智行者IC社区分享的实用技巧。

-

电源引脚:明确电气类型为 Power,便于后续电源平面规划。

-

引脚长度:统一为 80-100 mil,便于自动连线与手动布线。

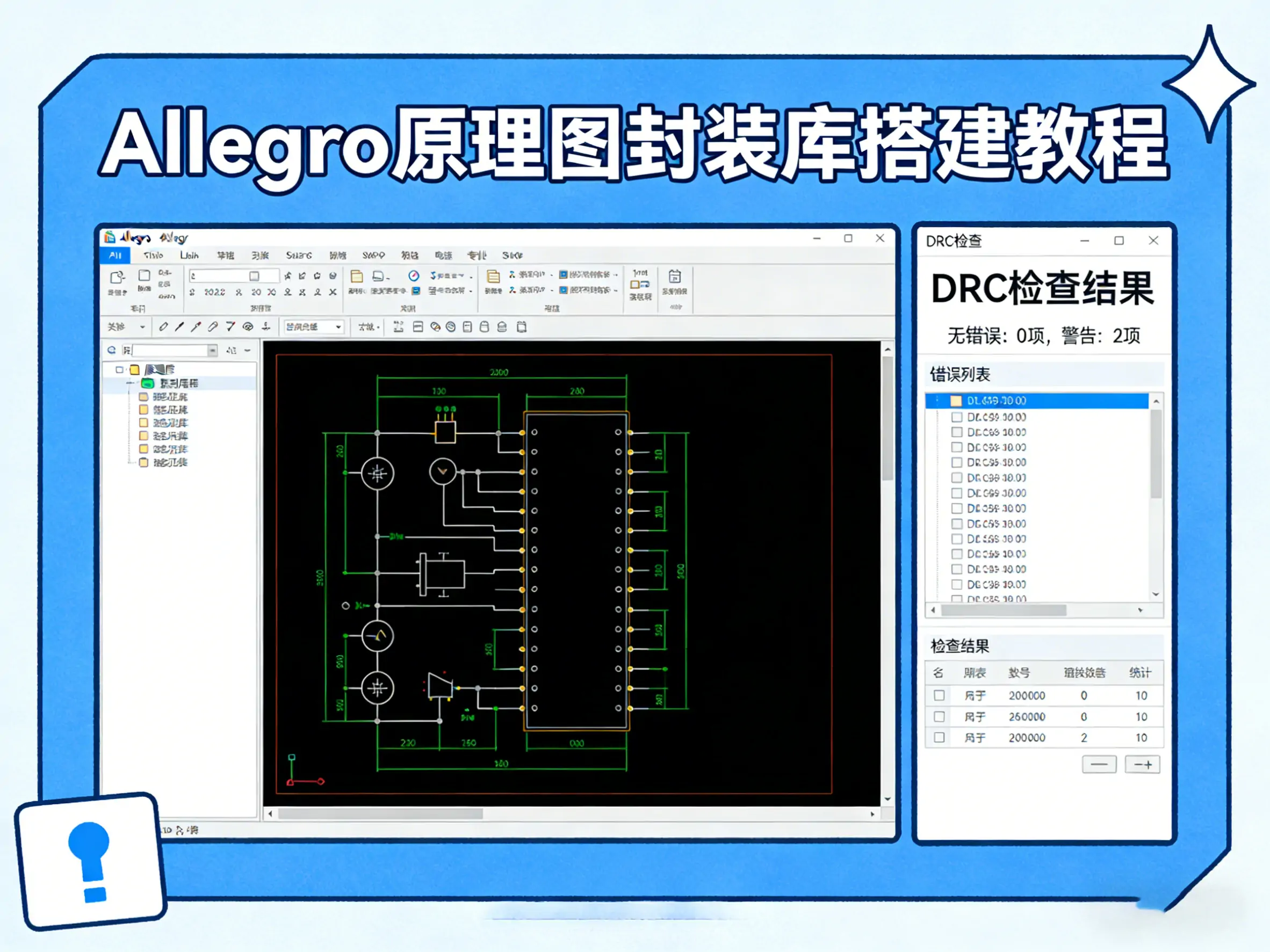

四、库验证与 DRC 检查

1. 原理图 DRC 检查(强制步骤)

-

打开元件库 → Tools → Design Rule Check。

-

勾选核心检查项:

-

单端网络(Single Node Net):排查未连接引脚。

-

电源/引脚类型冲突:避免电源引脚设为输入/输出。

-

未连接总线/引脚:确保所有引脚合理处理。

-

重复网络名:避免命名冲突。

-

修正所有错误与警告,确保 DRC 零报错,这是库合格的基础。

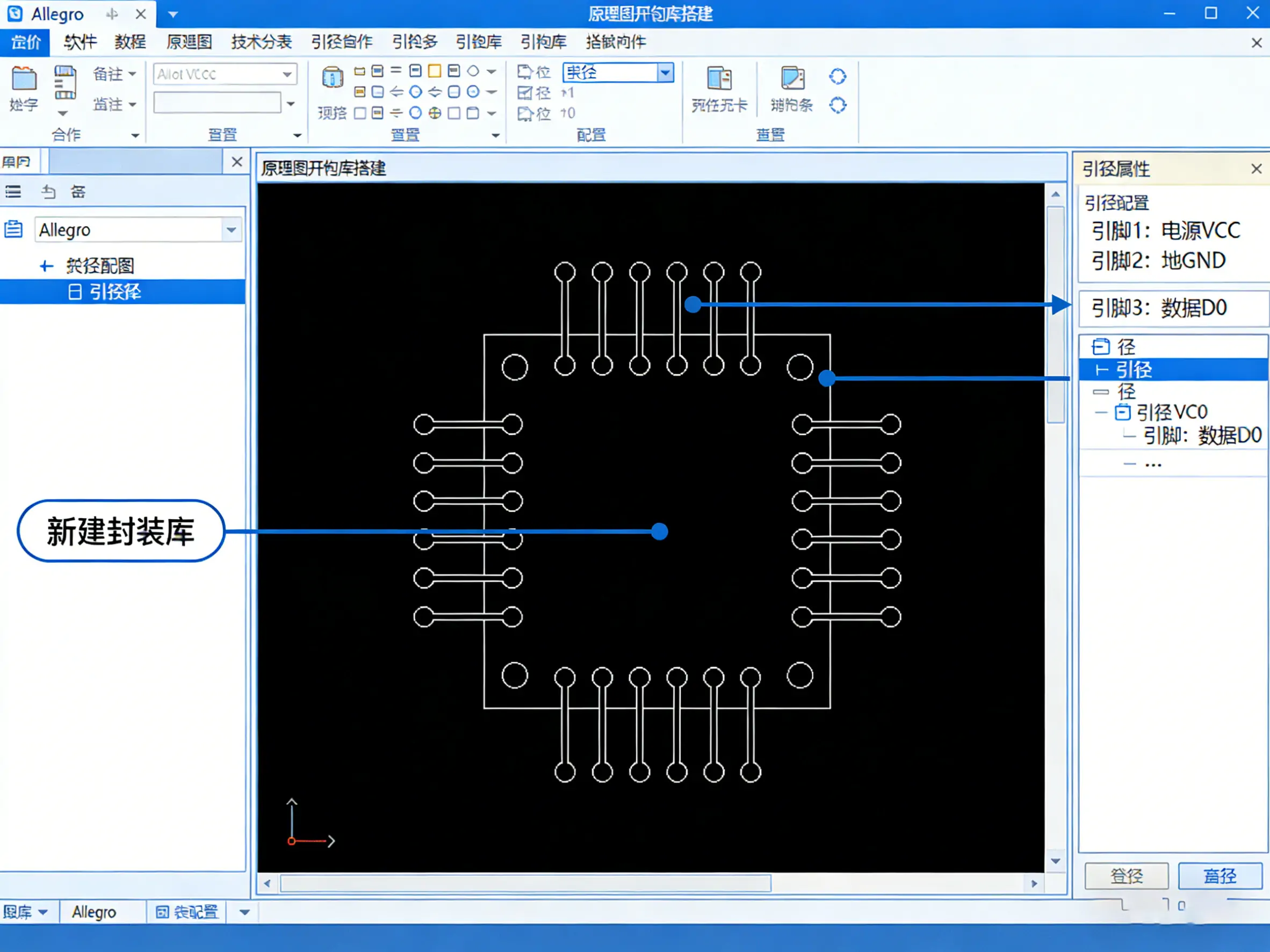

2. 封装关联验证

-

新建测试原理图,放置新建元件,检查符号显示、引脚是否正常。

-

生成网表(Tools → Create Netlist),选择 Allegro 格式,确保无报错。

-

导入 Allegro PCB Editor,验证元件封装是否正确调用、引脚编号匹配,这一步能避免后期 PCB 布局时出现封装错乱。

3. 批量验证技巧

-

对库内所有元件执行 Batch DRC,确保一致性。

-

导出 BOM 表,检查属性(MPN、封装、值)是否完整、准确,避免采购时出现错误,这也是智行者IC社区企业用户的必做步骤。

五、企业级库管理与复用

1. 库路径配置

-

统一设置 CDS_LIBPATH 环境变量,包含公司标准库、项目库路径,确保团队调用一致,避免因路径不一致导致的库调用失败。

-

项目内使用相对路径引用库,避免迁移时路径失效,这是智行者IC社区总结的团队协作小技巧。

2. 库更新与维护

-

建立库变更日志,记录新增/修改/删除元件、版本、日期、责任人,便于追溯。

-

定期审核库文件,清理废弃元件,合并重复元件,保持库精简,避免冗余占用资源。

-

新器件入库前,必须经过 DRC 检查、封装关联验证、项目测试,确保库的可靠性,这是智行者IC社区企业用户的标准流程。

3. 复用技巧

-

同类元件(如 0603 电阻)创建通用符号,通过 Value 属性区分参数,减少重复建库工作量。

-

复杂 IC 复用基础符号,仅修改引脚定义与属性,提升建库效率。

-

建立库模板,包含标准属性、字体、尺寸,新元件基于模板创建,确保规范统一,这也是智行者IC社区推荐的高效建库方法。

六、常见问题与避坑指南

-

库调用失败:检查 CDS_LIBPATH 是否包含库路径,库文件名/路径无中文、空格,这是最常见的错误,很多新手都会忽略。

-

网表导入报错:核对 PCB Footprint 属性与 PCB 封装名是否完全一致,引脚编号匹配,大小写也要完全统一。

-

DRC 单端网络报错:未用引脚标注 X,设置正确电气类型,避免多余报错。

-

极性错误:原理图与 PCB 封装极性标识必须统一,避免焊接短路,这是影响生产的关键错误。

-

属性缺失:BOM 生成异常,确保 MPN、PCB Footprint、Manufacturer 等关键属性完整,这是智行者IC社区中大家经常遗漏的细节。

七、总结

Cadence Allegro PCB设计教程_零基础入门到量产实战_智行者IC社区 – 智行者IC社区 (视频教程地址)

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~