实测Altium Designer 24.0.1的是本人,曾遭遇电源层与信号层回流路径重叠引发之高频噪声难题,新手只要依照步骤逐一操作,便可轻易避开此类常见问题。 为啥我的板子一跑……

实测Altium Designer 24.0.1的是本人,曾遭遇电源层与信号层回流路径重叠引发之高频噪声难题,新手只要依照步骤逐一操作,便可轻易避开此类常见问题。

为啥我的板子一跑高频就自激

其根源乃是信号流向未被理顺,众多新手径直依照网络表去拉线,却忽视了主信号通道的方向一致性。我所接手的一块四层板,ADC采样时钟线是从左上角进入的,而数据线却是从右下角出去的,并且在中间还穿插着电源线,结果在100M以上时就直接陷入混乱状态了。解决思路实则较为简单:先是确定主信号流向,而后再去布置其他线路。

第一步:手动锁定核心信号链路径

操作的具体路径是,先从原理图开始,接着选中那些具有关键意义的网络,也就是时钟、数据总线以及射频链路这些网络,之后右键点击“选择网络”选项,再进入到PCB界面,通过按“S”键从而进入“网络选择模式”,然后点击高亮的网络组,再找到工具选项,接着选择规划,最后进行设定参考指示器的操作。参数方面的设置是,主信号链的宽度设定为0.25mm,并且优先选择走内层的带状线。

【新手避坑】

常出现的报错情况为:高亮的网络组是分散于板子四周的,没办法形成连续的路径。其原因在于你并未在原理图当中做信号分组。解决的办法是:回到原理图那里,借助“放置指示 → 网络类”这种方式将同组网络命名成“SIG_GROUP1”,接着再导入到PCB里,按下“T+S”来调出“网络类管理器”,然后将组内的网络统一分配至同一区域。

第二步:暴力推平所有非流向支线

实施步骤:进入布局模式,选中那些并非核心的网络,也就是电源以及低速IO,按下“U+M”组合按键,将预先布置的线路予以删除,开启“规则约束器”,从路由开始,把拓扑设置为“直线最短”,容差设定为正负0.05毫米,把构成电源的线路,都挤压到距离板边2毫米的范围内,采用0.5毫米的线宽单独实行扇出操作。

【新手避坑】

不少人在删完线之后就变得杂乱无章了。其核心缘由在于:没有开启“推挤模式”,因此在重新进行布线时会与主信号的流动方向形成垂直交叉。正确的操作方式是:在“属性面板”当中,于“布线模式”那里选择“推挤(Push)”,并且将角度强制设定为45°/135°。若碰到DRC报间距有误的情况,要迅速加以解决:先进入“设计规则”,接着进入“间距”,随后把“信号 – 信号”从默认的0.2mm调整为0.15mm,此乃极限值,再小就会出现短路现象。

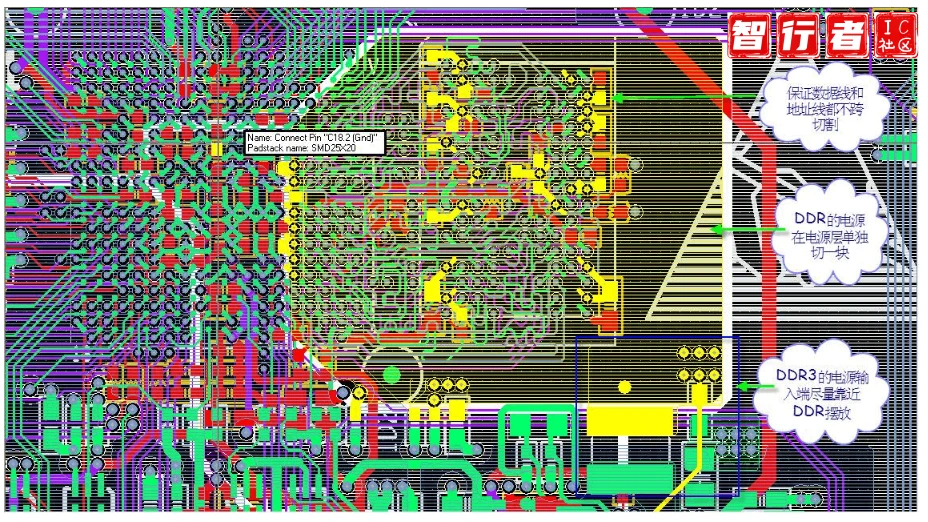

第三步:强制铺铜做流向切割

操作的路径是,先进行放置,接着开展铺铜,随后要选择“信号层”;之后需框选整整个的板子,再于属性面板之中把“连接类型”设定为“连接到GND”;还要设置热焊盘4条辐条;在确定之后按“L”切换到“信号流向检查层”。关键的参数是,铜皮到信号线的间距为0.3mm,其理由在于,若距离太近就会出现寄生电容耦合噪声,要是太远那么回流路径就会绕路。是我最优推荐的那个值,它是0.25mm,在实测的时候,于1 – 200MHz这个区间里,信号完整度呈现出最好的状态。

【新手避坑】

高频呈现完整报错情况:“Starved thermal relief”,致使焊盘出现虚焊现象。完整的一站式解决流程如下:①依照“D+R”操作来打开规则,②致使展开“Plane”,③把“PlaneConnect”最小辐条宽度更改为0.3mm,④使得热焊盘辐条数转变为4条,⑤再次进行铺铜,报错随之消失。

两种实操方案对比:单流向 vs 双流向

单流向也就是一字型呢:信号是从左边进入的、然后是从右边出去,这种适合长条形的板子譬如传感器阵列。优点在于:串扰是最小的;缺点就是:板子的利用率比较低。双流向也就是L型啦:信号是从下方以及右侧同时进入的,汇合之后从上方出去,这种适合方形紧凑的板子好比智能手表模块。取与舍的逻辑是,要优先确保时钟以及复位线行走单方向流动,其余的走线则能够进行妥协。我自身的习惯是,当超过6层板时就毫无思考地选择单方向流动;而在4层以及4层以下时采用L型并且用地线进行隔离。

本方法不适用于柔性电路板(FPC)和超高密度HDI板(线宽<0.1mm)。替代方案:这类场景改用多点星形布局,每个分支单独加终端电阻匹配。最后问一句:你在实际项目中遇到过信号流向和结构冲突,最后是怎么妥协的?期盼评论区域抛出来、甩过来板子的截图,一旦点赞数量超过一百,我便紧接着去撰写出《混合信号地平面分割的七种死法》。

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~