本人实实在在地测试过 Polar Si9000 V6.0 ,经历过因介质厚度算错从而致使实测阻抗仅仅只有 85Ω的情况,新手只要依照步骤一个一个地去操作,便能够轻轻松松地避开这类常……

本人实实在在地测试过 Polar Si9000 V6.0 ,经历过因介质厚度算错从而致使实测阻抗仅仅只有 85Ω的情况,新手只要依照步骤一个一个地去操作,便能够轻轻松松地避开这类常见的问题。

1 设置层叠结构与材料参数

将Polar Si9000开启,挑选模型“Edge-Coupled Surface Microstrip 1B”。于“Substrate 1 Height”处键入4.2mil,于“Dielectric Constant”处键入4.2,于“Trace Width(W)”处键入6mil,于“Trace Spacing(S)”处键入5mil,于“Trace Thickness(T)”处键入1.4mil(此为1oz铜厚),单位恒定为mil。

【新手需避坑】,常见的报错情况为,计算得出的阻抗呈现NaN或者无穷大的显示状态。其核心的原因在于,介电常数或者厚度的单位选择出现错误,也就是mil与mm产生了混淆的状况。具备快速解决的办法,要去检查单位设置,还要确认H单位与实际板厂保持一致,并且推荐整个过程当中全部使用mil。

2 运行计算并优化线宽线距

轻触“Calculate”按钮,读取“Odd Mode Impedance”数值。要是偏离90Ω,点击“Target Impedance”输入90,勾选“Optimize W”或者手动去调整W/S值,反复进行计算直至结果处于90±5%范围之内。设定固定目标值为90Ω,允许误差为±5%。

【新手需避坑】,存在常见报错情况:需计算的值一直处于92至93Ω之间,无法向下调整。其核心原因在于:忽略了阻焊层覆盖所带来的影响,阻焊油墨的介电常数约为3.5,这增加了容性。快速解决的办法是:在Model当中增加“Solder Mask”层,务必将其厚度设定为0.5至1mil,之后重新进行计算。

3 导出走线规则并对应PCB约束

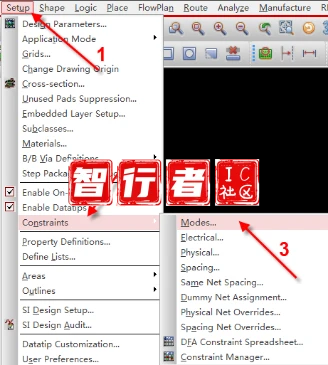

牢记最终呈现的W取值为5.8mil、S取值为4.8mil这两个数值,转换至PCB设计软件,像Allegro 17.4这类软件,开启Constraint Manager,寻觅差分对,调整“Line Width”为5.8mil,将“Primary Gap”设定成4.8mil,把“Neck Gap”准许放宽到8mil,对固定数值进行同步设置。

新手需避开的坑,常见的报错情况是,PCB走线完成进行测试时阻抗呈现出不连续的状况,并且在拐角的地方出现突变情形。问题的核心原因在于,没有去设置圆弧拐角或者拐角之间的间距过于接近。能够快速解决该问题的办法是,在约束里面将“Corner Style”设置为Arc,而且差分对内等长误差不能超过5mil,在拐角处致使S间距保持不变。

实测超过5mil会致使共模噪声增加3dB,会让眼图预张开度下降,因为90Ω差分对共模抑制要求极高,所以关键参数推荐值是,差分对内耦合长度方向上的等长误差推荐值≤2mil。

两种方案进行对比,方案A,也就是共面波导结构G-S-S-G,其抗干扰性能良好,然而插入损耗较大,它适用于像笔记本主板那样拥挤的板,方案B,即普通微带无包地,它的损耗较低,不过容易产生串扰,适合如开发板那样的净空区。对于USB 3.0高速信号而言,优先选择方案A,而HDMI 1.4信号则可以采用方案B。

一站式解决高频完整报错:出现报错“TDR测试在过孔处出现从50Ω跌落到70Ω的凸起”。流程如下:首先在Allegro中Highlight该过孔,接着检查过孔反焊盘直径是否大于或等于28mil,若小于该数值则将其改大,然后删除过孔无用残桩(Backdrill深度L小于或等于10mil),之后重新进行层叠计算,把过孔段等效阻抗提高至90Ω,最后重新流片。整个过程5分钟即可解决。

对于四层板以上的内层差分线而言,本方法并不适用,因为这会因压合流胶致使介电常数不均。存在简易的替代方案,即运用Si9000的“Embedded Microstrip”模型,且采用多层层叠平均介电常数法。你在调试90Ω阻抗的时候,是否碰到过什么奇特的报错呢?欢迎在评论区分享,记得点赞收藏本品以防止下次遭遇困境。

微信扫一扫

微信扫一扫

还没有评论呢,快来抢沙发~